市面上的关于信号完整性的书籍,开篇概述信号完整性的内容部分,老wu总结了一下,大概都是这样描述的:

在时钟频率只有10 MHz的年代,电路板或封装设计的主要挑战就是如何在双层板上布通所有信号线,以及如何在组装时不破坏封装。由于互连线并未影响过系统性能,所以互连线本身的电气特性并不重要。在这种意义下,可以说“对信号而言,过去的互连线是畅通透明的”。

但是,现在的时钟频率提高了,信号上升边也已普遍变短。对于大多数电子产品而言,当时钟频率超过100 MHz或上升边小于1纳秒时,信号完整性效应就变得重要了,通常将这种情况称为高频领域或高速领域。这些术语意味着在互连线对信号不再透明的产品与系统中,如果不小心处理就可能出现一种或多种信号完整性问题。

总结一下,在“低速”时代,互连线是“畅通透明的”,我们不用管信号完整性问题,只要把线拉通就好,甚至是在面包板上用杜邦线把元器件连起来电路都能很好的工作。

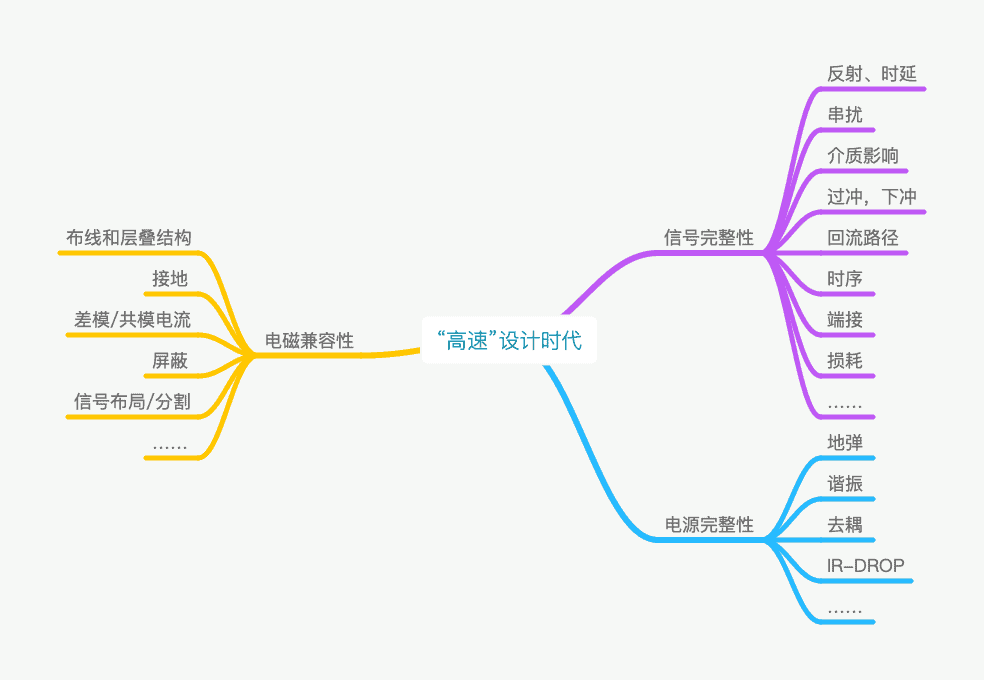

而“高速”时代,我们布线时就要通盘考虑:

1.信号完整性

2.电源完整性

3.电磁兼容性

等因素。

在“高速”时代,PCB设计如果在开始阶段不考虑信号完整性,就很难做到首件产品一次成功。

进一步细化上边罗列的“信号完整性”、“电源完整性”、“电磁兼容性”术语,又能推出更多新的术语:

Ok,那“低速”时代是怎样演变为“高速”时代的?怎样界定“低速”和“高速”,他们之间有过渡阶段吗?还是“低速”啪的一下就跨越进入到了“高速”时代?

让我们回滚一下时间轴,回顾一下信号完整性的发展过程,我们可以将信号完整性的发展过程在时间轴上划分为4个阶段,分别考虑不同的关注点:

阶段1:只要把线拉通就行的“透明”连接阶段

互连线对产品电性能的影响以及互连线是否透明取决于下边三个参数的组合:

1、信号的上升时间

2、互连线的长度

3、噪声容限

只要有足够长的上升时间或足够短的互连线,所有的互连线对信号都是透明的。

我们知道计算(机|器)的发展有四个阶段:

- 手动阶段

- 机械阶段

- 机电阶段

- 电子阶段

电流磁效应的发现打开了电应用的新领域,1830年美国科学家约瑟夫·亨利在其独立研究中发现了法拉第电磁感应定律,比法拉第更早发现这一定律,可惜没有发表,然后于1835年发明了电子继电器,继电器的发明也是电磁学的重要应用之一,分别在电报和电话领域发挥了重要作用。

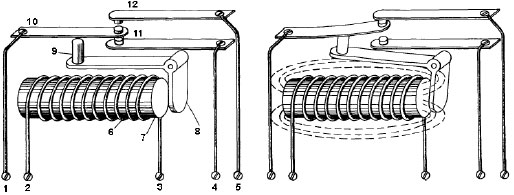

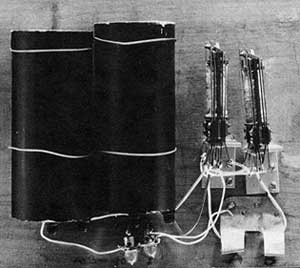

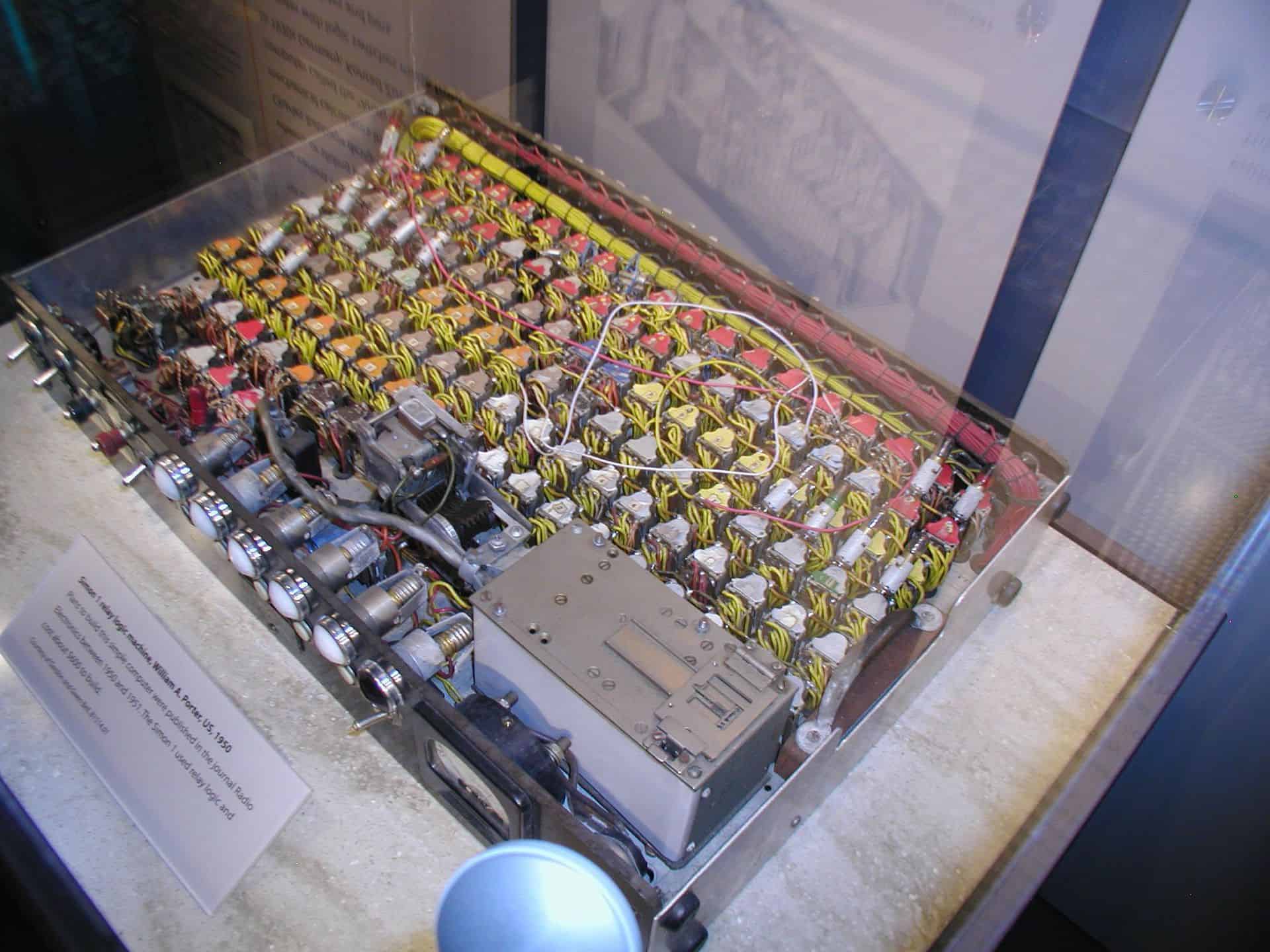

继电器计算机的诞生

1937年11月的一个傍晚,贝尔实验室的一位研究数学家George Stibitz离开办公室准备回家,他从贝尔实验室的仓库里拿了两个电话继电器、几个手电筒灯泡、一根电线和一个干电池。在家里,他坐在厨房的桌子后面,开始组装一个简单的逻辑装置,该装置由上述部件和一个由锡罐制成的开关组成,啪的一下就做好了,很快啊。

这被证明是第一个继电器二进制加法器,其中一个点亮的灯泡代表二进制数字 “1”,另一个不亮的灯泡则代表二进制数字 “0”。他的妻子多萝西娅(Dorothea)以“厨房桌子”(kitchen table)的名字命名它为K-model。这就是继电器计算机的雏形。

在贝尔实验室的支持下,1940年初,继电器计算器M-1成功运行,它使用了440个继电器,可以解决当时贝尔实验室做电学研究中面对的大量复数的加减乘除四则运算问题,一次复数乘法需大约30~45秒,但比人工使用机械计算器的15分钟相比已是很大的进步。但重要的是它开创了一个时代,也即数字计算机时代。

机械继电器的输出的响应时间最快也在10ms级别,理论上继电器1秒能切换状态100次,也就是100Hz的频率,这相比于人工操作的机械计算器来说,已经很快了,但以现在的眼光来看,这就是真•低速时代。

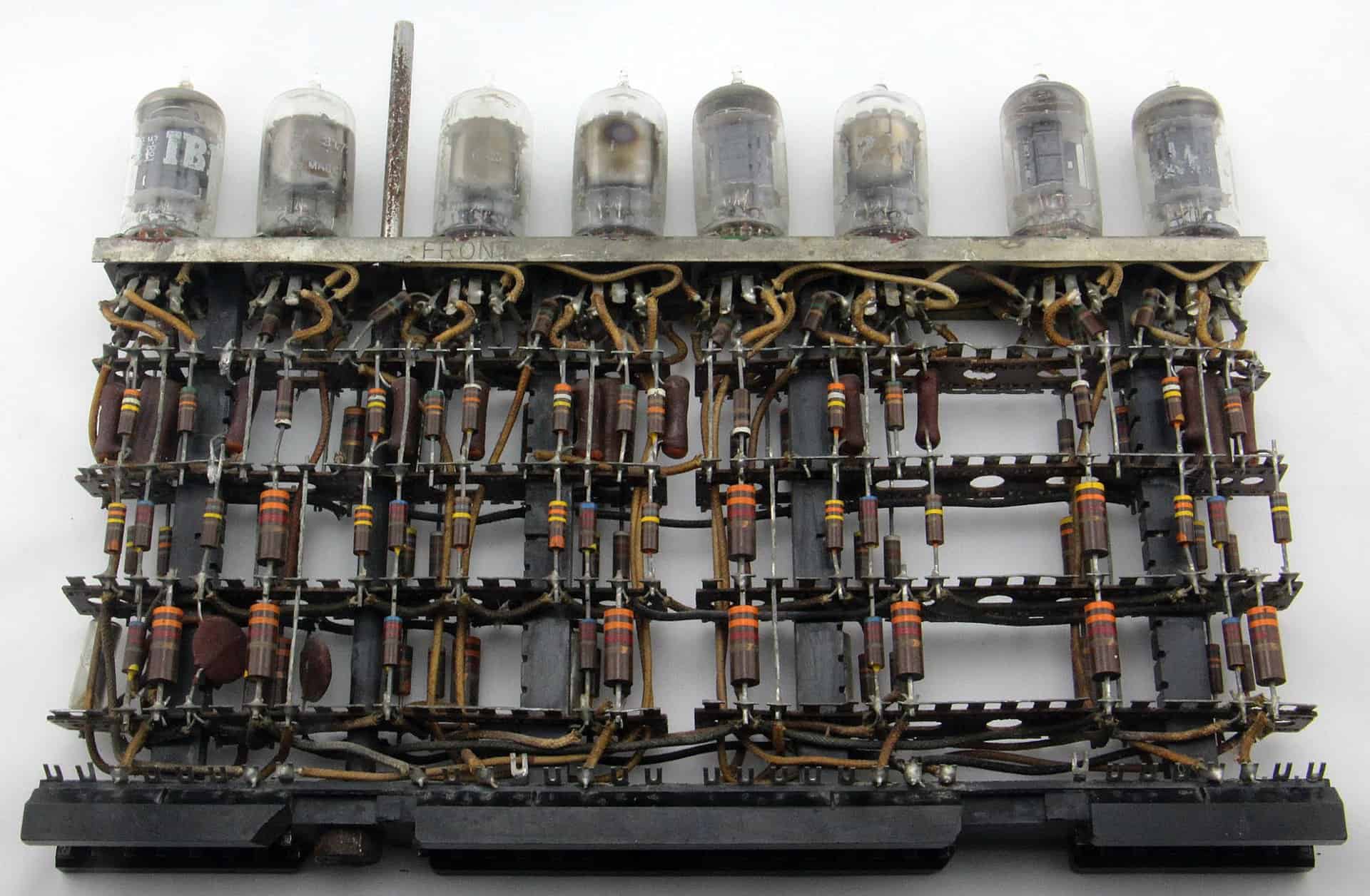

如上图的继电器计算装置所示,只要把线接通就行,那时可连PCB都还没有的。

为什么继电器之间的互联线不会造成信号完整性问题?

让我们打开频域之眼,以频域的视角来分析这个缘由。

次奥,频域,看到这个词就不由得开始害怕,捋了捋头上的头发,专栏怕是要看不下了了吧 😂

我们讨厌频域,老wu也讨厌频域,对于PCB设计工程师或者数字电路设计工程师来说,我们更喜欢在时域里思考问题,我们平时接触的也是像示波器、逻辑分析仪之类的分析设备,而频谱仪或者矢量网络分析仪平时很少接触甚至连摸都没摸过。

老wu在专栏的【PCB的发展历史】章节有提到,詹姆斯·克拉克·麦克斯韦1864年发表的论文《电磁场的动力学理论》,将电、磁、光统归为电磁场中现象,提出了著名的麦克斯韦方程组,建立了第一个完整的电磁学理论体系,为电磁学在生产生活中应用奠定了强大的理论基础。

物理世界的行为与麦克斯韦方程的预测是完全一致的,如果我们将量子力学加入到与麦克斯韦方程的原理中,也就是所谓的量子电动力学(QED),我们最终会得到一个真实世界的模型。

信号与互连线基于其电磁特性进行交互,当然也完全遵循于量子电动力学。如果我们理解了麦克斯韦关于电磁理论的方法,我们便可以想象信号在传输线中传播时发生了什么。有了理论上的支撑,可以提升我们设计的直觉,如果一个问题可以通过直觉来识别,那么我们就可以快速定位问题的根源,而无需花费大量时间进行各种试错。

不小心扯远了,关于时域/频率的更详细话题,老wu在后续的专栏里再进行描述。

这里说回为什么继电器计算机的互联不会造成信号完整性问题。

让我们将视角切到频域,在频域的世界,它不是真实的,而是一个数学构造。时域是唯一客观存在的域,而频域是一个遵循特定规则的数学世界,正弦波是频域中唯一存在的波形,这是频域中最重要的法则,即正弦波是频域的语言。工程师们通常选择在频域中使用正弦波,是因为时域中的任何波形都可用正弦波合成。这是正弦波的一个非常重要的性质。[1]

通过傅里叶变换,可以将时域中的周期性的方波,描述为不同频率正弦波的集合。

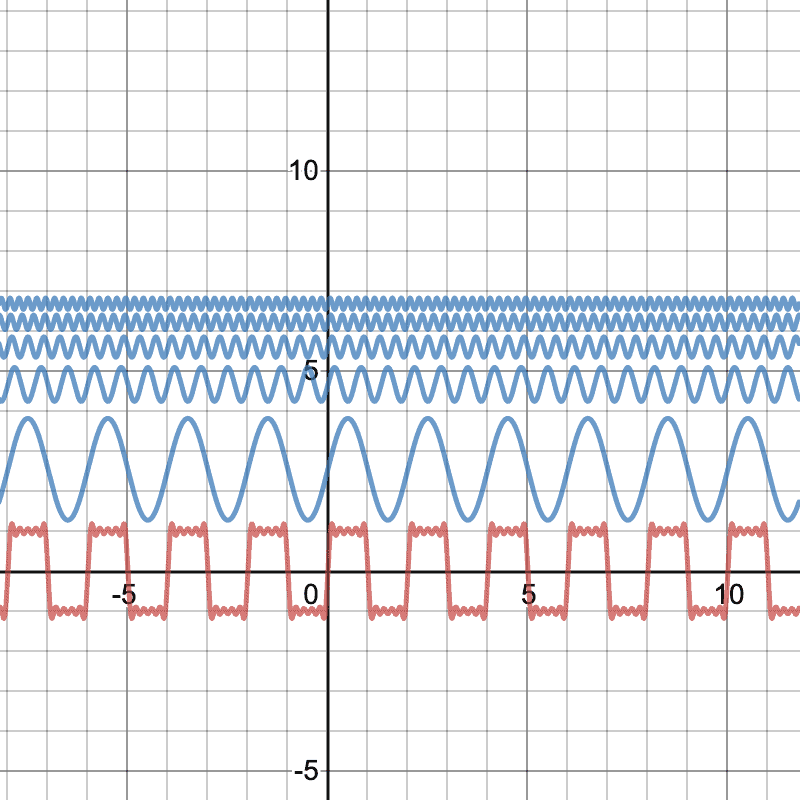

下边是周期性的占空比为50%的方波的谐波合成的desmos演示

在频域中,唯一需要讨论的就是正弦波,时域中的任何波形都可以用不同的频率、不同的幅度的正弦波合成,在时域中可能需要成千上万个电压-时间数据点表示的波形,在频域中则变换成为一个幅度-频率数据点,对于若干个频率点,其幅值的集合成为频谱。

下边的动图很好地说明了时域中方波如何分解成若干个正弦波,然后合成频谱图的。

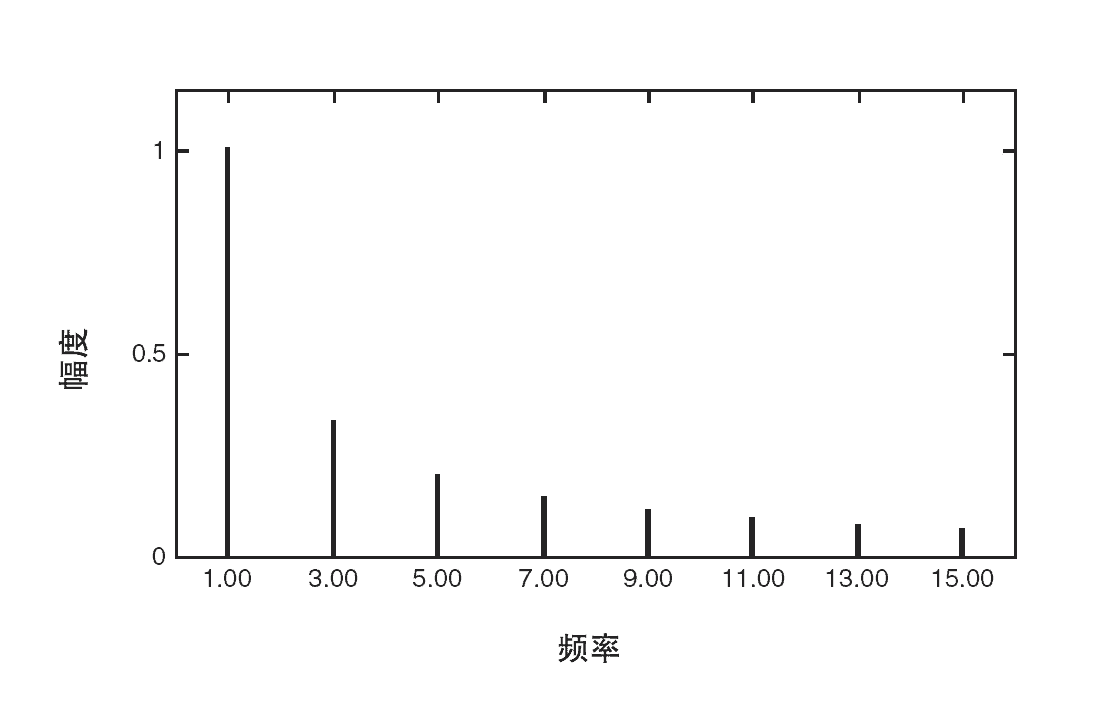

信号的傅里叶变换表示法也被称为该信号的频谱。频谱是信号的频域表示,它是用频率来描述的信号。你可以把频谱看作是信号的图形,振幅在y轴上,频率在x轴上。一个完美的理想方波的频谱如下图所示。

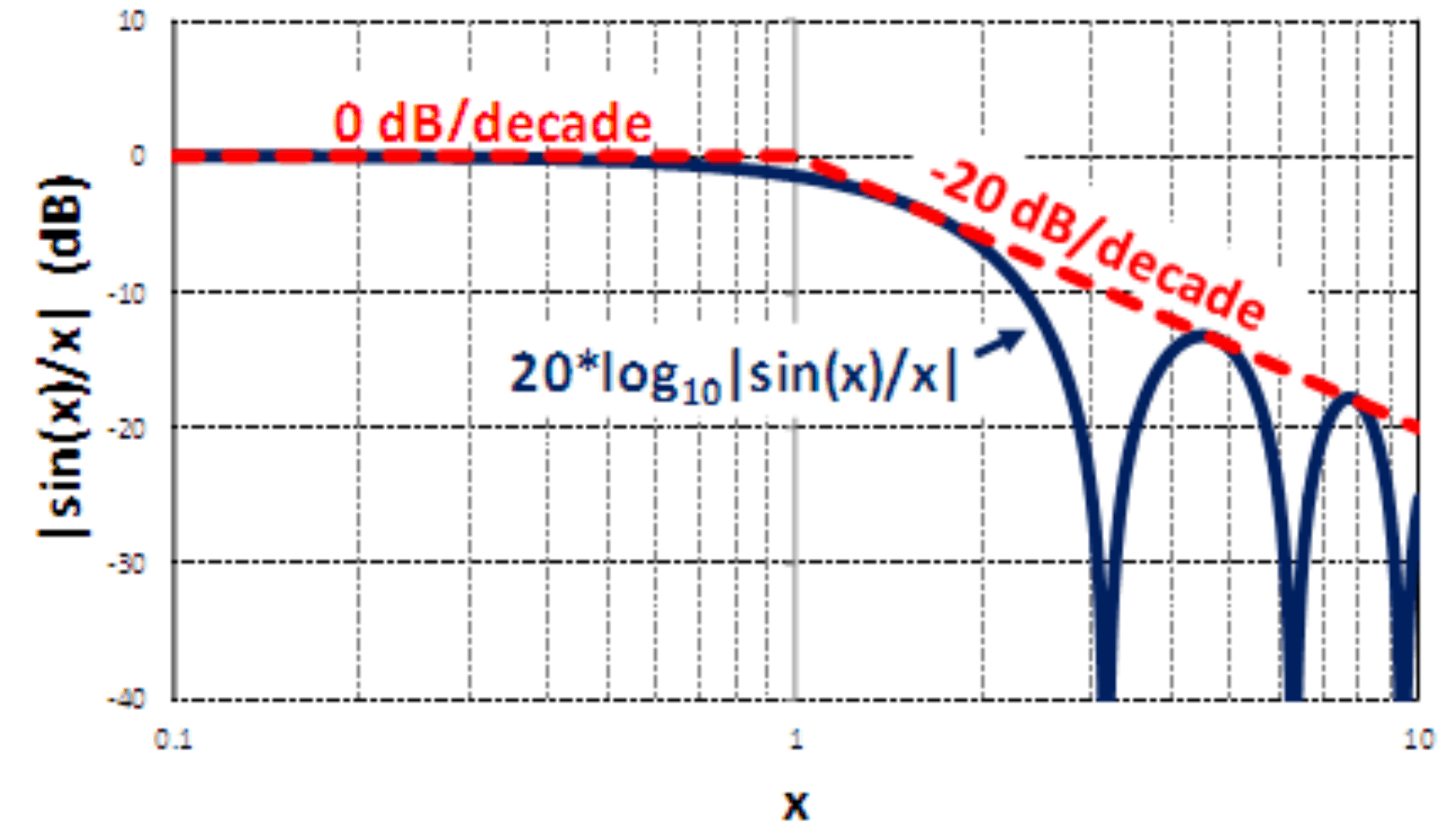

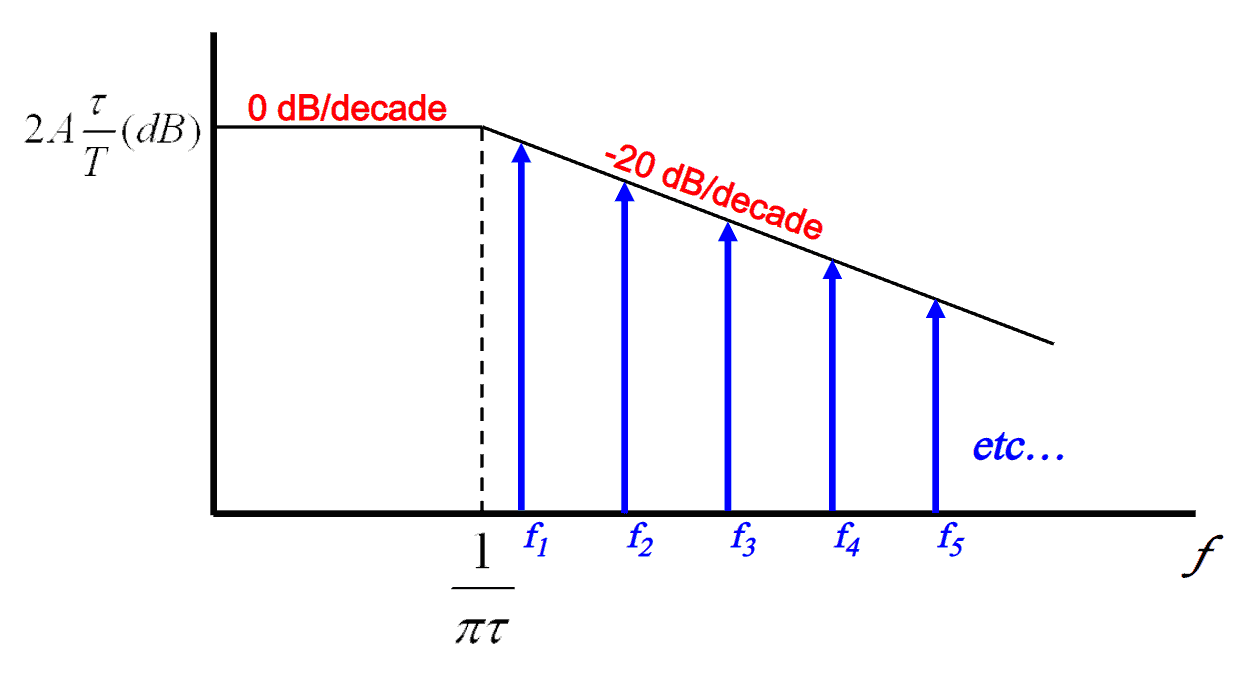

画出该离散频谱的包络图则:

理想方波频谱包络渐近线如下:

观察理想方波频谱包络渐近线图,我们发现在X轴,也即标识频率的这个轴向,有个1/Πτ,(这里τ为脉冲宽度)。

什么意思呢,这里的1/Πτ为拐点频率,在这个频率之前,包络的幅度基本不变,而在该频率点之后,包络幅度以-20/dB 10倍频程的斜率下降。

但在现实世界中,理想方波是不存在的,实际信号的上升时间不可能为0。对于CMOS工艺的输出驱动器,不论是PMOS还是 NMOS管,其状态转换都需要一定的时间。研究梯形波形的频谱特性有助于我们深入了解时域表示和频域表示之间的关系。另外,当我们研究数字系统的EMC或信号完整性问题时,梯形波形更加贴近于常见数字信号波形的频谱特性,也很有用处。

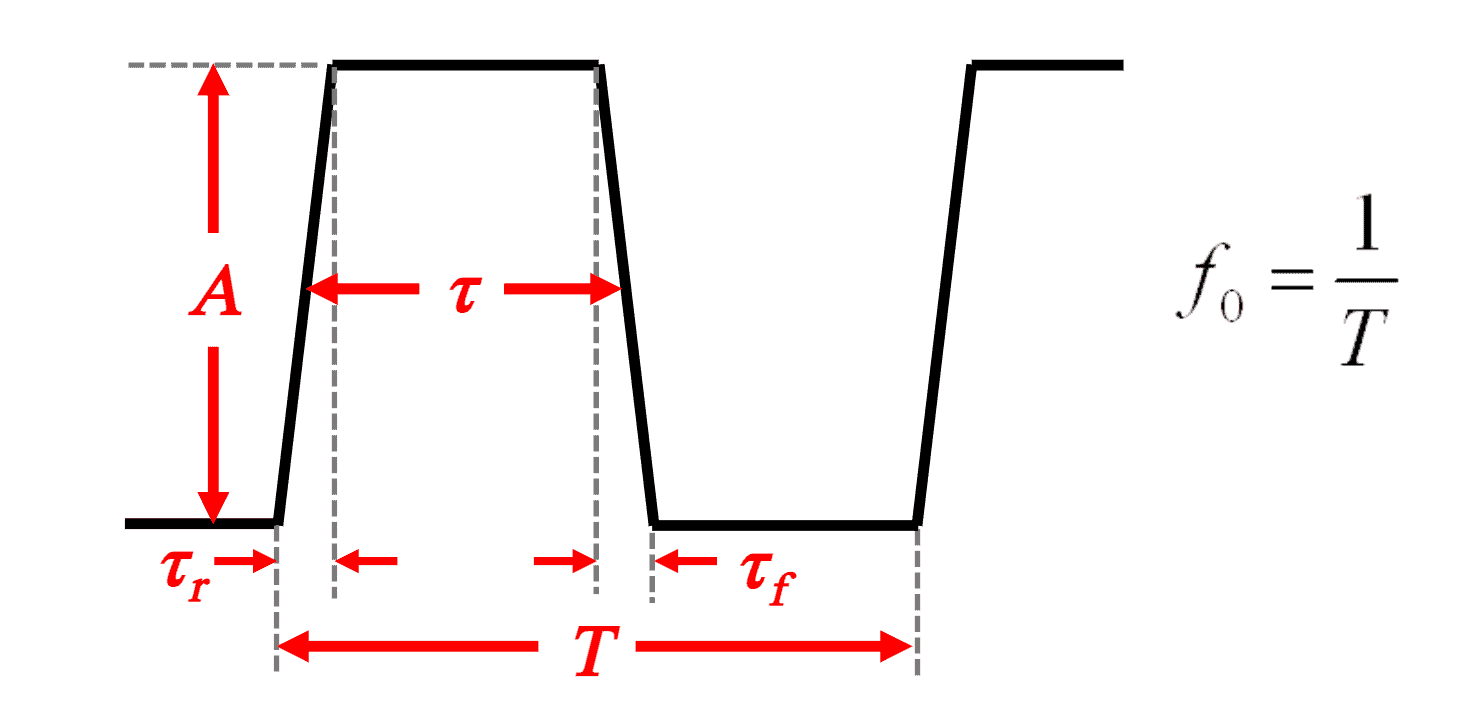

一个典型的梯形脉冲的时域波形表示如下:

相关的参数:周期T(因此,是基频),幅度A,上升时间τr,下降时间τ f以及导通时间或脉冲宽度τ,频率f0=1/T。

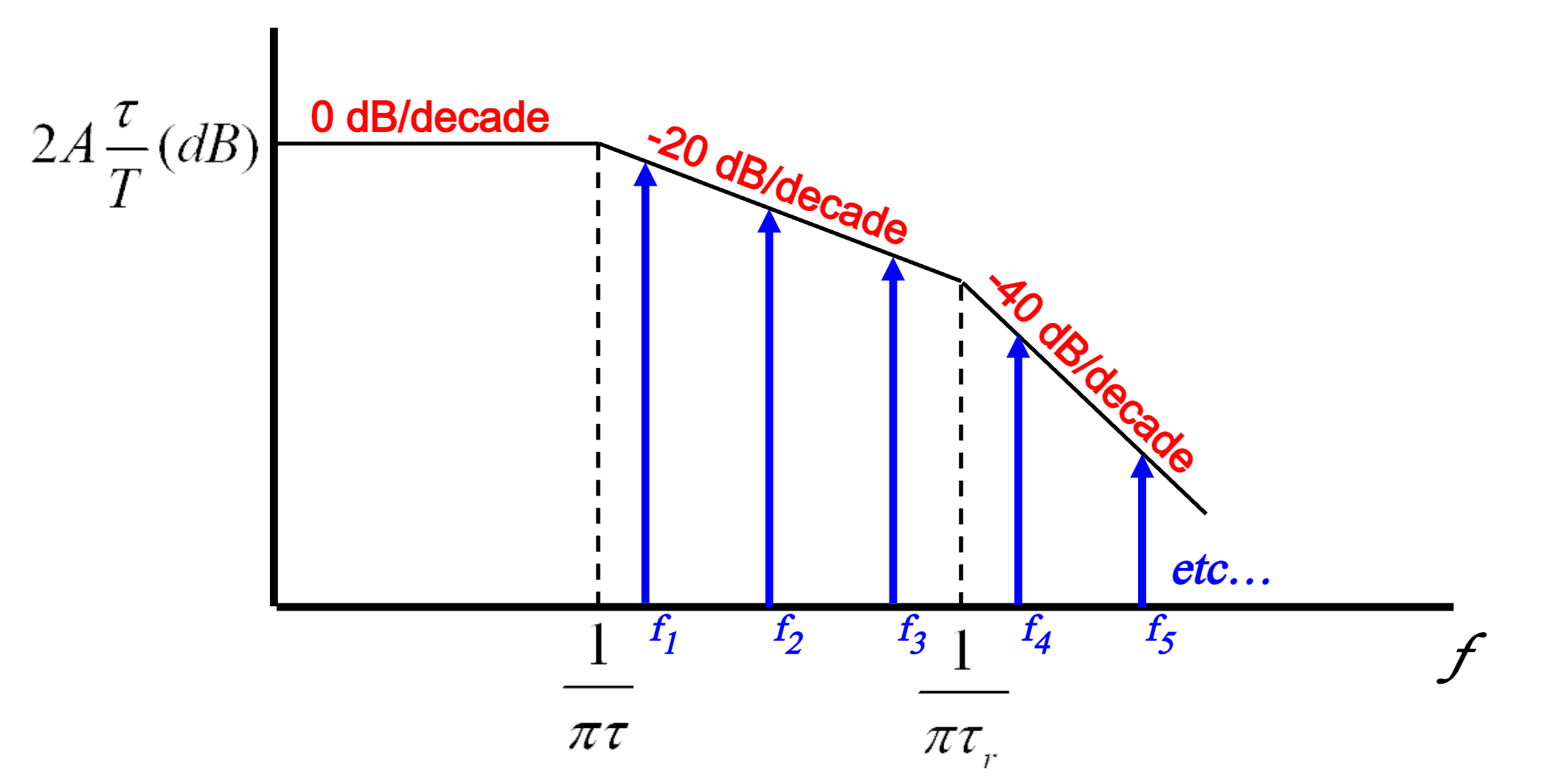

相对于理想方波的频谱,这里有两个非常有意思的拐点,一个是1/πτ,另一个是1/πτr。频谱分量的幅度经第一个转折点后以-20dB/10倍频程的速度下降,经第二转折点后以-40dB/10倍频程的速度下降。

第一个拐点与信号脉冲宽度τ有关,而第二个拐点与上升时间tr有关。

从上边的梯形波频谱包络图我们可以推导出:

对于EMC设计而言

- 信号的频率越高,脉冲宽度τ值就越小。因此,1/πτ拐点向较高频率侧偏移,产生更多噪声。

- 随着上升时间变短,τr值变小,1/πτr拐点朝着较高频率侧偏移,产生更多噪声。

要设计噪声更少的电路,应避免上述这些情况,使1/πτ拐点和1/πτr拐点向低频侧偏移是比较有利的。也即减小信号周期频率及加大信号上升/下降时间。

对于信号完整性设计而言

1/πτr这个点是个关键点,其与信号的上升/下降沿时间τr有关,1/πτr往右,即朝着更高频的方向,频谱幅度以-40dB/10倍频程迅速下降,也就是这个点往右的更高次谐波的能量对于完整呈现信号的原貌的贡献已经不大,因为数字信号处理的是0和1,我们并不需要原原本本地完美还原信号波形,只要信号失真不太大,不造成信号识别错误就可以接受。所以,我们的互联线的带宽只要大于1/πτr就问题不大,那比1/πτr大到底大多少够呢?

1/πτr ≈ 0.3183/τr,工程上给的经验值是0.35/τr或者0.5/τr。

这个频率就是我们信号完整性所关注的最高频率。

由于机械继电器的响应时间为10ms级别,所以梯形波的脉冲宽度τ占主导因素,这里即使继电器翻转时的信号上升时间tr很短,周期信号也不会有较高电平的高次谐波噪声,不会造成EMC问题。

当然,继电器的电磁吸合与释放,有可能造成EMI问题,但在1940年代,这还不问题。

然后,我们再看一下互联线所需的带宽,也即机械继电器信号上升下降沿时间τr。

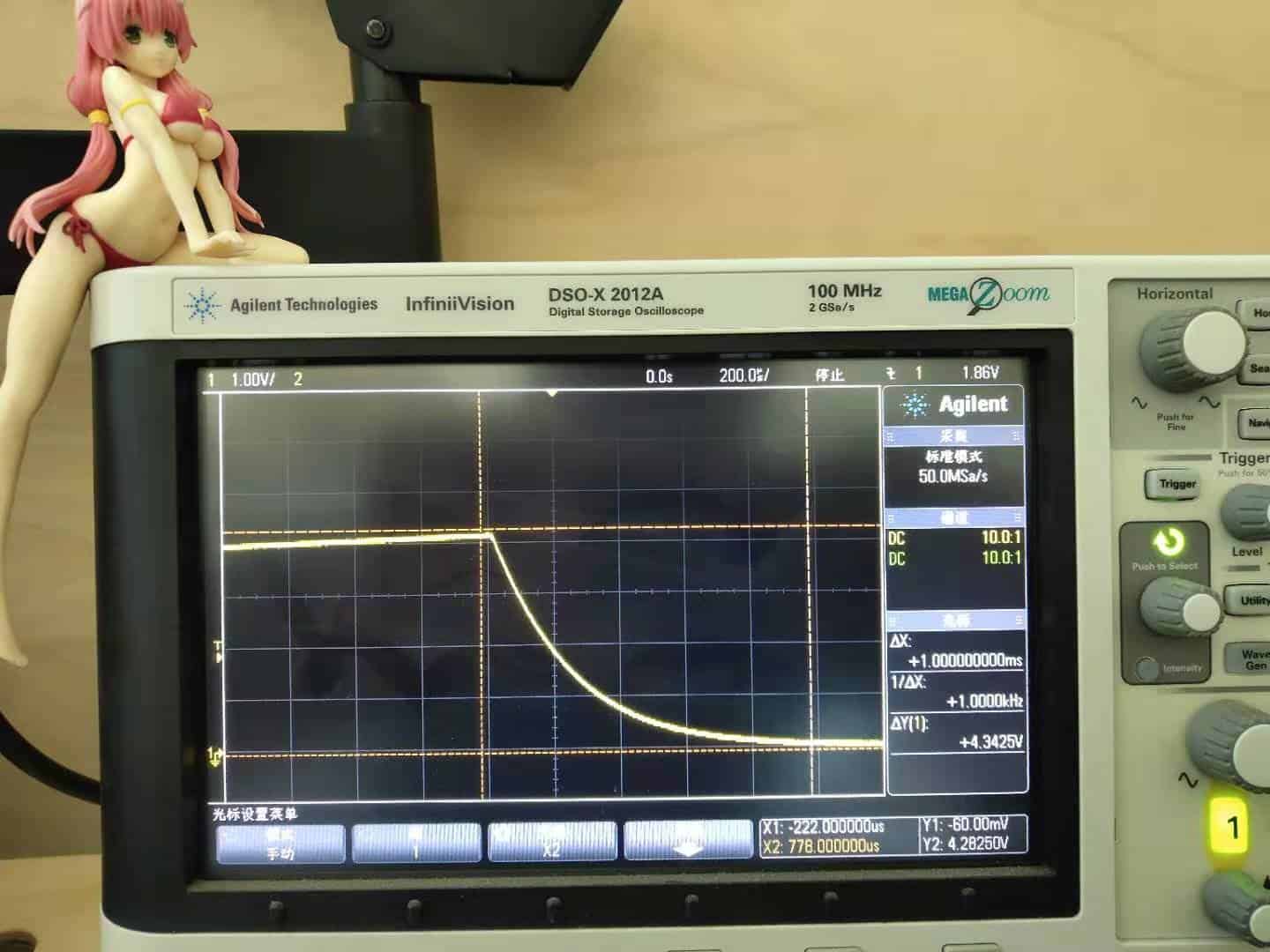

上图是老wu用示波器测得得电磁继电器的信号下降沿时间,大约为1ms。

上升/下降沿时间按80%来取值,则为800 us,换算成频率约1250Hz ,真•低频 😄

这里有个传输线何时“透明”的经验法则就是传输线长度<带宽所对应波长的1/10长度时,我们可以认为电路是电小尺寸。

电尺寸用波长来衡量。波长代表了为使相位改变360°, 正弦电磁波必须走过的距离。严格地讲,这只适用于一类电磁波:均匀平面波。但是, 其他类型的电磁波也有类似的特性,所以这个概念也是通用的。

虽然麦克斯韦方程可以解释所有的电现象,但从数学上来讲它们是相当复杂的。因此,在可能的情况下,就使用较简单的近似方法,如集总参数电路模型和基尔霍夫定律。 存在一个重要问题:当分析问题时,何时可以用简单的集总参数电路模型和基尔霍夫定律来代替麦克斯韦方程。基本的回答是,当电路的最大尺寸为电小尺寸时,例如,远小于电源激励频率所对应的波长时。通常使用一个准则,即当电路的最大尺寸小于波长的 1/10时,认为电路是电小尺寸。[2]

所以,对于继电器计算机这种信号上升/下降沿时间为1ms的互联,只要电路尺寸远小于38.5公里就可以当作“透明”!

当然,继电器的噪声容限也是很强悍的,我们需要很大的能量来维持继电器ON的状态,老wu测了一下,一个普通5V继电器,它的线圈导通状态功耗达到了0.4W,换句话说,普通的辐射干扰的能量不足以让继电器改变其工作状态。

当然,继电器计算机有很多的弊端,比如状态切换速度太慢,功耗还很大,更要命的是体积没法做小,很快就被开关速度更快的电子管计算机所替代了,到了1950年代,电子管计算机开始处于统治地位。

电子管显然比继电器要快得多,因为它没有机械部件的移动,只有电子流来进行开关状态的切换。电子管的开关切换速度达到了4微秒级别,比10毫秒级别的机械继电器快了近2500倍!

电子管的信号周期可以达到250KHz,信号上升/下降沿时间为:1us,换算成FR4 PCB上的1/10波长电尺寸约为:4282 cm!

电子管计算机的互联依然可以是为“透明”

1947年12月,美国贝尔实验室的肖克利、巴丁和布拉顿组成的研究小组研发出了晶体管,发热量较低体积更小巧的晶体管从50年代开始大量取代电子管的地位,电子计算机开始进入到了晶体管时代,1958年:仙童公司Robert Noyce与德仪公司基尔比间隔数月分别发明了集成电路,开创了世界微电子学的历史。

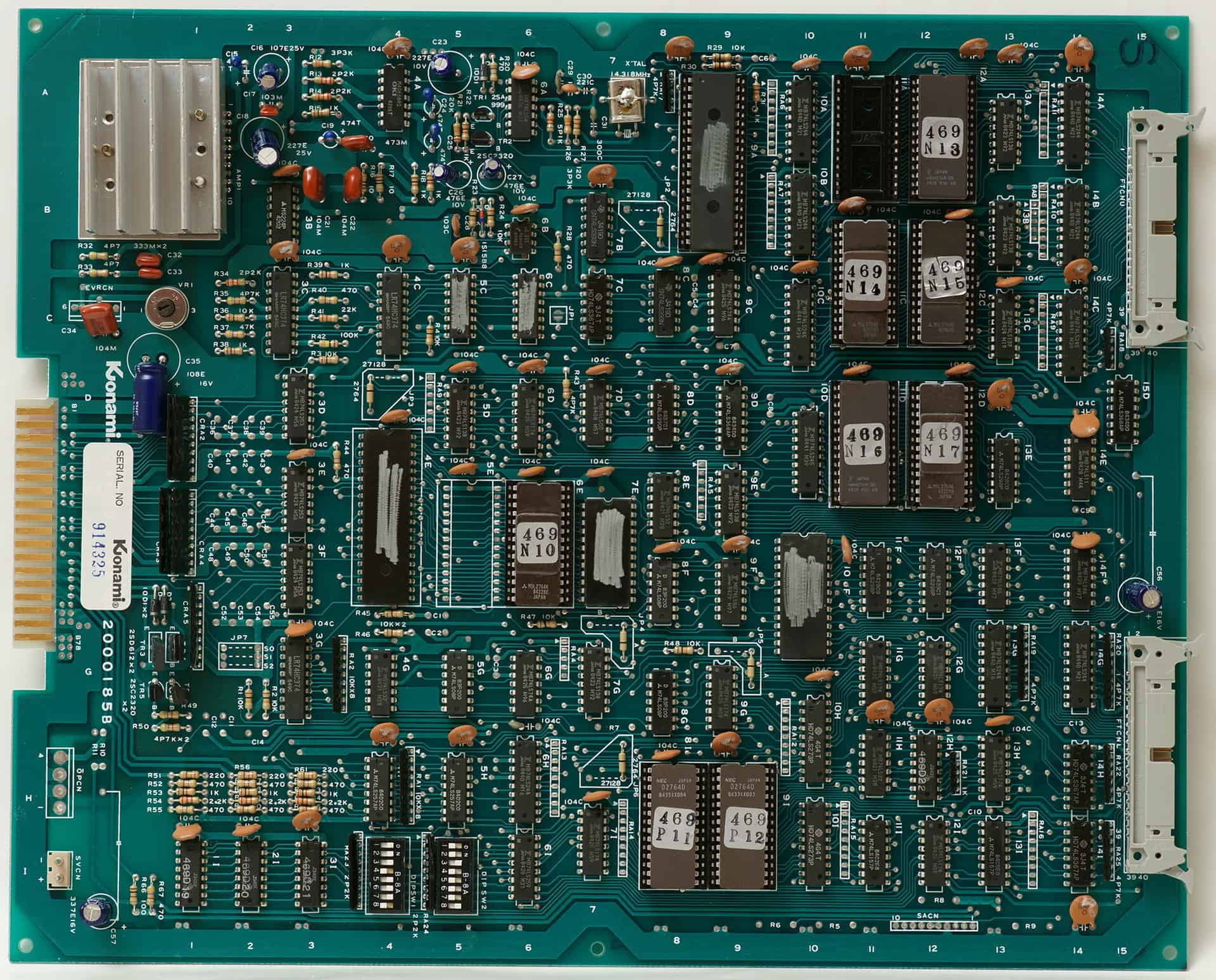

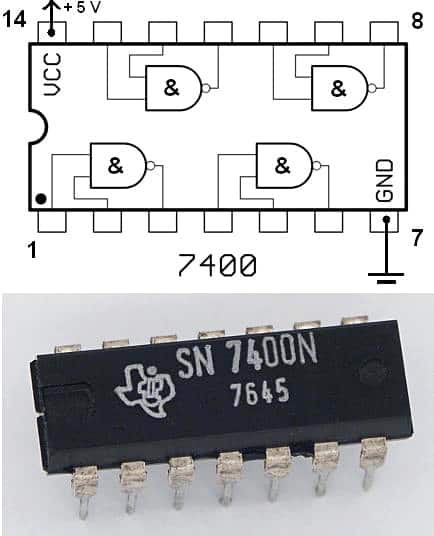

晶体管-晶体管逻辑(英语:Transistor-Transistor Logic,缩写为TTL)也由德州仪器开发出来,比如我们所熟悉的74XX系列。

TTL最大时钟频率可达 8.3 MHz,信号上升/下降沿时间为:30ns,换算成FR4 PCB上的1/10波长电尺寸约为:128cm。注意,这里单位来到了厘米级别!

而不久之后,CMOS逻辑也问世了,开始与TTL分庭抗礼,在初期两者相比较TTL主要是速度快,CMOS则是速度慢,但省电、成本比TTL低。只要速度不是首要考虑的场景,更多应用会偏向于选择CMOS。但随着CMOS技术的进步,其反应速度也已经超越TTL。

早期的CMOS逻辑的最大时钟频率可达 3.6 MHz,信号上升/下降沿时间为:70ns。

这时候无论是TTL还是更慢一点的CMOS,互联都还是“透明”,当时的PCB设计也是把线拉通了就好了。工程师们除了担心逻辑门本身的时间延迟外,什么都不用担心,可以忽略电线延迟和任何看起来像传输线效应的东西。这是最好的一种逻辑。

不需要很高深的电路和电磁学的知识,人们只需要把时序和布线搞好,实在布不通了,就飞线伺候,产品都能可靠地工作。正是集成电路逻辑的这种特性,造成了20世纪80年代和90年代的计算机热潮。除了要保证别把线接短路了,然后电源功率有一定的余量来维持运转外,不需要担心其它电气方面的事情。

参考资料:

[1] Eric Bogatin,《信号完整性与电源完整性分析(第3版)》,电子工业出版社, pp. 30–35.[2] Clayton R.Paul ,《电磁兼容导论 第2版》 ,人民邮电出版社, pp. 9–12.